2026-02-03T16:26:00Z

Aşağıdaki makele x.com/damnang2 adlı kullanıcının yazdığı ingilizce makaleden alınarak AI yardımı ile çevirilmiş ve kontrol edilmiştir. Giriş kısımından önce gerekli olabilecek terimler gene ai yardımı ile açıklanmış ve kontrol edilmiştir.

Sözlük

HBM (High Bandwidth Memory): TSV ile birbirine bağlanmış, dikey olarak istiflenmiş (3D) DRAM yapısı. AI ve HPC uygulamaları için çok yüksek bant genişliği sağlar.

DFT (Design for Test): Chip tasarımında test edilebilirliği artırmak için eklenen mimari ve devre teknikleri.

Memory Testing: Memory hücrelerine veri yazıp geri okuyarak hatalı hücreleri tespit etme süreci.

Stuck-at-0 / Stuck-at-1 Fault: Bir bit hücresinin sürekli 0 veya sürekli 1 değeri vermesi.

Coupling Fault: Bir memory hücresindeki işlemin başka bir hücreyi etkilemesiyle oluşan hata.

March Algorithms: Memory testinde kullanılan adres sıralı test algoritmaları ailesi. Stuck-at, Transition ve Coupling Fault’ları tespit eder.

March C-: Yaygın kullanılan bir March algoritması türü. Birden fazla fault şeklini kapsar.

VDR (Voltage Drop Retention) Test: Çalışma voltajı düşürülerek retention zayıf hücrelerin tespit edilmesi.

MBIST (Memory Built-In Self-Test): Memory testinin chip içinde, at-speed şekilde yapılmasını sağlayan donanım.

ATE (Automatic Test Equipment): Chip’leri harici olarak test eden test cihazları. Hız ve erişim açısından sınırlıdır.

Memory Repair: Üretimde oluşan hatalı row/column’ların spare row/column ile değiştirilmesi.

Redundancy: Memory içinde bulunan yedek row/column yapıları.

RA (Redundancy Analysis): Hangi spare row/column’un hangi hatayı kapatacağını belirleyen algoritma.

BIRA (Built-In Redundancy Analysis): RA işlemini chip içinde yapan mekanizma.

BISR (Built-In Self-Repair): BIRA sonucuna göre repair bilgisini fuse/eFuse/OTP ile uygulayan yapı.

ECC (Error Correction Code): Çalışma sırasında oluşan geçici (soft) hataları tespit ve düzeltir.

SECDED: ECC türü; 1-bit hatayı düzeltir, 2-bit hatayı tespit eder.

On-Die ECC: ECC mantığının memory die içinde yer alması. HBM3 ve sonrası için zorunludur.

GO / NO-GO Test: Memory’nin temel olarak çalışıp çalışmadığını hızlıca belirleyen test.

Bitmap Test: Her bit için ayrı Pass/Fail bilgisi üreten detaylı test.

Failure Analysis için kullanılır.

FA (Failure Analysis): Hata kök nedenlerini analiz etmeye yönelik detaylı inceleme süreci.

KGD (Known Good Die): Stacking öncesi testten geçmiş, sağlam olduğu doğrulanmış DRAM die.

TSV (Through-Silicon Via): 3D memory’de die’lar arasında dikey elektriksel bağlantı sağlayan yapı.

Base Die: HBM stack’in en altındaki die. Üst die’lara test ve erişim bu katman üzerinden yapılır.

Interposer: HBM ile GPU/AI accelerator arasında sinyal ve güç dağıtımını sağlayan ara katman.

System-Level Test: HBM, host chip’e bağlandıktan sonra yapılan son aşama testler.

Yield: Üretimde sağlam çıkan ürün oranı. HBM’de KGD × stacking × system integration yield çarpımıyla belirlenir.

Giriş

AI çağına girerken, HBM (High Bandwidth Memory) öncülüğünde memory’nin önemi hiç olmadığı kadar arttı. NVIDIA, AMD gibi firmaların AI semiconductor’ları, HBM olmadan tam performansına ulaşamaz.

Peki bu memory’ler nasıl test ediliyor?

Doktora çalışmalarımı yürüttüğüm laboratuvar, semiconductor testing alanında Design for Test (DFT) odaklı çalışıyor ve memory testing & repair konusunda dünyanın en saygın araştırma gruplarından biriydi.

Bu yazıda, doktora araştırmalarımdan ve endüstri deneyimimden yola çıkarak memory test metodolojisinin temellerini, teknik olmayanların da anlayabileceği şekilde anlatacağım.

1. Memory Testing Nedir?

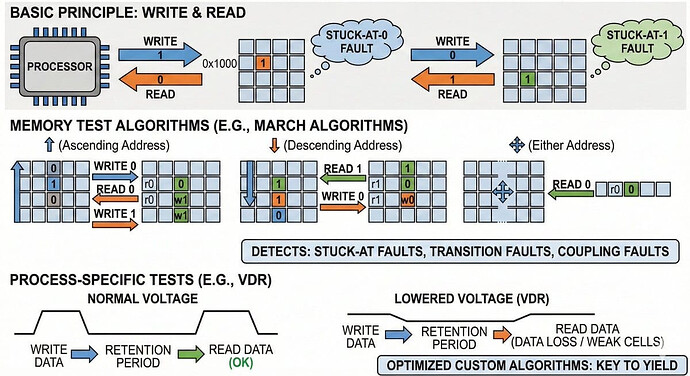

Temel Prensip: Write & Read

Memory testing’in en temel prensibi basittir:

Belirli bir address’e bir değer yazılır (write), sonra geri okunur (read) ve yazılan değerle okunan değer karşılaştırılır.

Eğer değerler farklıysa, o bit cell fault’lu kabul edilir.

Örneğin:

-

Address

0x1000’e1yazıp0okunuyorsa → Stuck-at-0 fault -

0yazıp1okunuyorsa → Stuck-at-1 fault

Memory Test Algorithms

Ancak yalnızca tüm hücrelere 0 ve 1 yazıp okumak tüm fault tiplerini yakalamaya yetmez.

Memory cell’ler arası etkileşimden doğan Coupling Faults gibi hatalar için sistematik algoritmalar gerekir.

Bu noktada March algorithms devreye girer.

March C-, March LR, March SS gibi birçok varyant vardır ve her biri farklı fault tiplerini hedefler.

March algoritmalarının temel yapısı:

-

⇑ (Ascending): Address’ler 0’dan sona doğru artarak

-

⇓ (Descending): Sondan 0’a doğru azalarak

-

⇕ (Either): Her iki yönde

Örneğin March C- algoritması şu 6 adımdan oluşur:

{⇕(w0); ⇑(r0,w1); ⇑(r1,w0); ⇓(r0,w1); ⇓(r1,w0); ⇕(r0)}

Bu algoritma:

-

Stuck-at Faults

-

Transition Faults

-

Bazı Coupling Faults

tespit edebilir.

Process-Specific Test Algorithm’ler

Standart March algoritmalarına ek olarak, memory’nin fiziksel karakteristiğini dikkate alan özel testler de vardır.

Buna örnek olarak VDR (Voltage Drop Retention) testleri verilebilir.

Bu testlerde çalışma voltajı bilinçli olarak düşürülür ve retention zayıf olan hücreler elenir.

Normal voltajda çalışan ama düşük voltajda fail olan marginal cell’ler, genellikle sahada görülen intermittent failure’ların kaynağıdır.

Gerçek üretimde defect’ler çoğu zaman:

-

belirli region’larda,

-

belirli koşullarda,

-

process’e özgü şekilde

yoğunlaşır.

Bu yüzden firmalar process-tailored test pattern’ler geliştirir.

Sonuç olarak, bir firmanın yield rekabetçiliğini belirleyen şey; process defect karakteristiğini ne kadar iyi anlayıp, buna uygun custom test algorithm’lere sahip olduğudur.

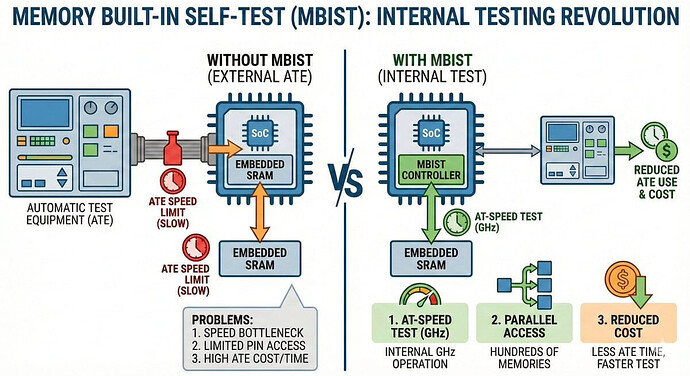

2. MBIST Neden Gereklidir?

MBIST (Memory Built-In Self-Test), memory test devrelerinin chip içine gömülmesini sağlar ve ATE kullanımını minimize eder.

Peki neden memory’yi doğrudan ATE ile test etmiyoruz?

1) Speed

ATE ile testte, ATE–chip arayüzü hız sınırlayıcıdır.

Modern SoC’lerde embedded SRAM’ler GHz hızlarında çalışır; dış tester’lar bu hıza yetişemez.

MBIST, At-Speed testing yapılmasını sağlar.

2) Accessibility

Modern SoC’lerde yüzlerce memory block vardır.

Hepsine dış pin’ler üzerinden erişmek fiziksel olarak imkânsızdır.

MBIST, IJTAG veya IEEE 1500 gibi internal test structure’lar üzerinden tüm memory’lere erişir.

3) Cost

ATE süresinin kısalması test maliyetini düşürür.

MBIST ile birden fazla memory parallel test edilebilir.

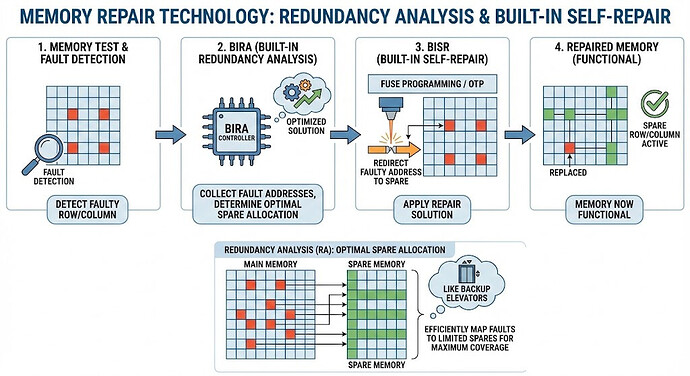

3. Memory Repair Nedir?

Logic’ten farklı olarak memory, repair ile yield artırabilir.

Memory repair, defective row veya column’ların spare row/column ile değiştirilmesidir.

Bunu, binada ana asansör bozulunca yedek asansöre geçmeye benzetebiliriz.

Redundancy Analysis (RA)

RA, hangi spare row/column’un hangi defective bölgeyi değiştireceğini belirleyen algoritmadır.

Amaç:

-

sınırlı spare kaynağıyla,

-

mümkün olan en fazla defect’i kapatmaktır.

Örneğin:

Aynı column’da birden fazla defect varsa, row repair yerine column repair daha verimli olabilir.

BIRA ve BISR

-

BIRA (Built-In Redundancy Analysis):

Chip içinde çalışan ve test sırasında toplanan defect address’lerine göre en uygun repair planını çıkaran algoritma. -

BISR (Built-In Self-Repair):

BIRA’nın belirlediği repair bilgisini fiilen uygulayan mekanizma.

Genellikle fuse, eFuse veya OTP (One-Time Programmable) memory kullanılır.

4. ECC ile Memory Repair Arasındaki Fark

Her ikisi de memory defect’leri ele alır ama amaçları farklıdır.

-

Memory Repair:

Manufacturing sırasında oluşan Hard Faults’ları fiziksel olarak ortadan kaldırır.

Runtime overhead yoktur. -

ECC (Error Correction Code):

Çalışma sırasında oluşan Soft Errors’ları (cosmic ray, alpha particle kaynaklı bit flip) düzeltir.

En yaygın örnek SECDED’dir (1-bit correction, 2-bit detection).

HBM ve GDDR6’da iki teknoloji birlikte kullanılır.

HBM3 ile birlikte On-Die ECC zorunlu hale gelmiştir; stacked yapıdaki ek defect risklerini yönetmek için.

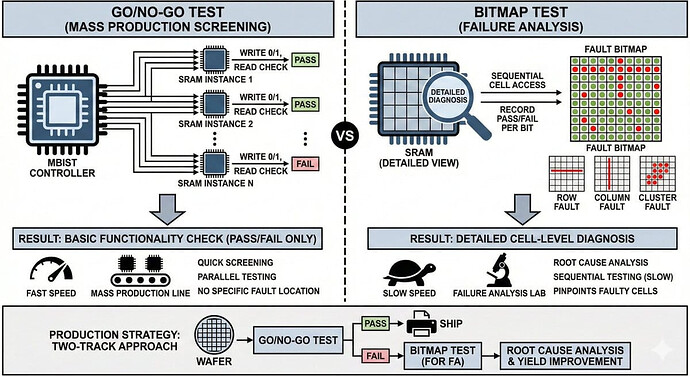

5. Gerçek Test Akışı: GO/NO-GO’dan Bitmap’e

GO/NO-GO Testing

İlk aşama hızlı taramadır.

Memory’nin çalışıp çalışmadığına bakılır (alive/dead).

Bu test:

-

Pass / Fail verir,

-

ama hangi bit’in bozuk olduğunu söylemez.

Bitmap Testing ve Sınırlamaları

GO/NO-GO fail olursa Bitmap testing yapılır.

Her bit için ayrı ayrı Pass/Fail bilgisi tutulur.

Avantajı: güçlü diagnostik.

Dezavantajı:

-

Parallel test yapılamaz

-

Büyük memory’lerde test süresi üstel artar

Bu yüzden production’da değil, Failure Analysis (FA) için kullanılır.

Bitmap sonuçları defect kökenini anlamada kritiktir:

-

Row/column yoğunluğu → decoder problemi

-

Cluster pattern → particle contamination

Memory Test Neden Logic Test’ten Sonra Yapılır?

-

MBIST controller logic’tir

Logic bozuksa MBIST güvenilir çalışmaz. -

Sonuç yorumlama netliği

Logic sağlam değilse memory fail’inin kaynağı anlaşılamaz. -

Yield stratejisi

Logic repair edilemez, memory repair edilebilir.

Önce logic yield’i garanti edilir.

6. HBM Testing: 3D Memory’nin Zorlukları

HBM, TSV (Through-Silicon Via) ile bağlanan 3D stacked DRAM yapısıdır.

Yield’in zor olmasının temel sebebi budur.

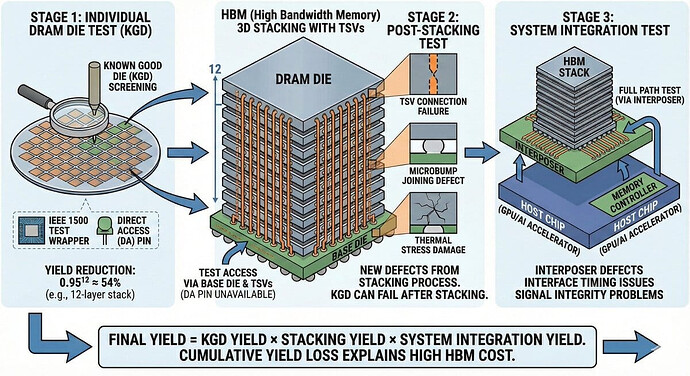

Stage 1: Individual DRAM Die Test (KGD)

Stacking öncesi her die test edilir → Known Good Die (KGD) seçilir.

Örnek:

12-layer HBM3E

Die yield = %95

Toplam yield ≈ 0.95¹² ≈ %54

Stage 2: Post-Stacking Test

Stacking sonrası:

-

TSV defect

-

micro bump defect

-

thermal stress kaynaklı defect

oluşabilir.

KGD bile stacking sonrası bozulabilir → retest zorunludur.

Stage 3: System-Level Test

HBM, GPU / AI accelerator’a bağlandıktan sonra test edilir.

Yeni riskler:

-

Interposer bonding defect

-

Timing issue

-

Signal integrity problemi

Son yield:

KGD yield × stacking yield × system integration yield

Bu yapı, HBM’nin neden pahalı olduğunu açıklar.

Sonuç

Memory testing & repair, semiconductor yield’ini belirleyen çekirdek teknolojilerdir.

Basit görünen “write & read” prensibinin üzerine:

-

March algorithms

-

MBIST

-

BIRA / BISR

-

ECC

katman katman eklenmiştir.

HBM çağında test karmaşıklığı hızla artmaktadır.

3D yapı, her aşamada yeni defect olasılıkları yaratır.

AI semiconductor pazarı büyüdükçe, memory test engineer’larının rolü kritikleşmektedir.

Daha hızlı, daha doğru ve daha verimli test teknolojileri, bir sonraki nesil AI accelerator’larını mümkün kılacaktır.