Geçtiğimiz 3 ayda çalıştığım bir konuya dair kısa bir şeyler yazmak istedim hem kayıt olması hem de bir ihtiyacı olan olursa diyerekten.

Çalıştığım konu Controller Area Network kısaca CAN olarak geçiyor. Başlıktan anlaşılacağı üzere bu bir bus yapısı ve çoğunlukla arabalarda ve otomasyon cihazlarda kullanılıyor. Güvenlik anlamında hiçbir özelliği olmadığı için gizli projelerde kullanımı tehlikeli olsa da herhangi bir gizliliği olmayan projelerde rahatlıkla kullanılabilir bir bus yapısı kendisi.

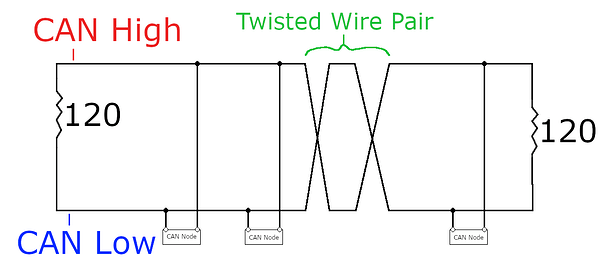

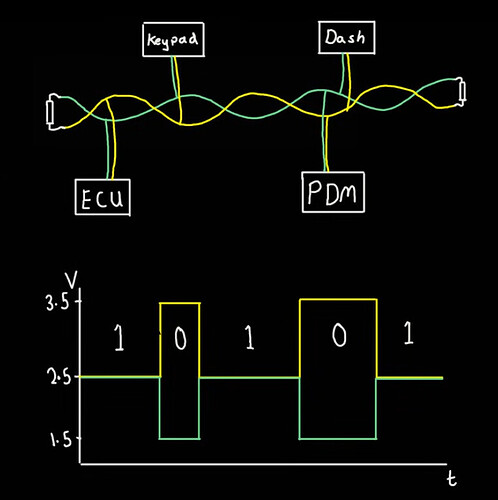

CAN differential pair kullanarak haberleşme sağlayan bir metod. Yukarıda göreceğiniz üzere iki adet kablomuz var bunlardan birisi CANL diğeri CANH bu iki kablo bütün iletişimin ve bus yapısının oluştuğu kısımdır. CANL ve CANH arasındaki gerilim farkı CAN PHY tarafından okunarak dijital sinyale dönüşüyor ve sonrasında alıcının RX portuna gönderiliyor. Gönderim yapılmak istediğinde ise sistem TX’den gelen dijital bilgiyi differential pair kullanarak bus’ta bulunan diğer alıcılara gönderiyor.

Gene yukarıda görüldüğü üzere CANL ve CANH arasında 120 Ohm luk bir direnç gözleniyor. Bir PHY satın aldığınızda bu direnç zaten PHY üzerinde oluyor ve bazılarında bu direnci inaktif hale getirebiliyorsunuz.

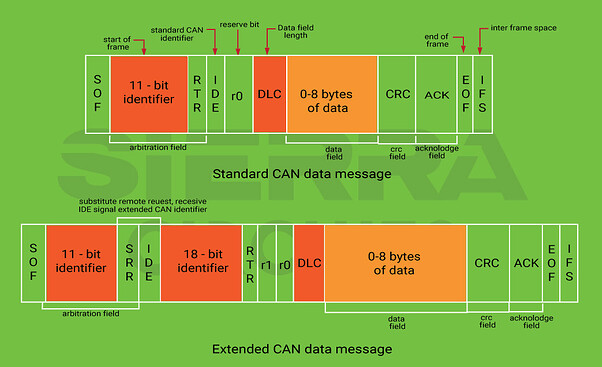

Can iletişim kurmak için yukarıda göreceğiniz paket formlarını kullanmakta. CAN 1.0 2.0-A 2.0-B ve CAN XL modları var. 2.0B 2.0A yı okuyabiliyor ancak tam tersi mümkün değil.

Projede çalışırken ilk defa register map üzerinden bir peripheral’ı kontrol edip yazılmış olan can IP’sini doğrulamaya çalıştım.

Doğrulama sırasında izlediğim metod adımları şu şekilde.

1- Öncelikle hazır testleri koştum

2- Vivado’da bulunan hazır can IP sinin test example’ını açtım ve verilen CAN IP’sini bu example’da bulunan BUS’a bağladım. BUS’da akan bilgiyi görene kadar üzerinde çalışarak sistemin nasıl çalıştığını anladım.

3- İki adet IP’yi birbirine bağladım ve aralarında iletişim kurulmasını sağlayacak kodu yazdım.

4- Hazırladığım iki IP’li modeli FPGA üzerinde koşmak için petalinux altyapısı kullandım ve komutları otomatik olarak IP’lere yazacak scripler yazdım.

5- FPGA üzerinde internal olarak doğrulama yaptım.

6- Externel olarak and kapısı kullanarak doğrulama yaptım.

7- Gene external olarak PHY kullanarak doğrulama yaptım.

8- Burası en kritik aşama: Hazır bir can modülü aldık ve bu can modülü kullanarak bus’a yazdığım bilgileri IP’ler üzerinde gördüm ve IP’lerden geri hazır modüle bilgi yazdırdım.

Sonuç olarak baştan sona driver yazmadan bir doğrulama yapmış oldum.